#### ESCOLA POLITÈCNICA SUPERIOR

# ESCOLA POLITÈCNICA SUPERIOR UNIVERSITAT DE LES ILLES BALEARS

## PROJECTE DE FINAL DE CARRERA

**Estudi:**

# Enginyeria Informàtica

Títol:

Construction of a Hardware Prototype of ReCANcentrate and Implementation of a Media Management Driver for the Nodes of the Prototype

**Alumne: David Gessner**

Directors : Julián Proenza Arenas Manuel Alejandro Barranco González

Data: Novembre de 2010

Fem constar que el projecte de final de carrera titulat *Construction* of a hardware prototype of ReCANcentrate and implementation of a media management driver for the nodes of the prototype ha estat realitzat, sota la direcció de Julián Proenza Arenas i Manuel Alejandro Barranco González, per David Gessner. Així mateix declaram que el projecte està finalitzat i preparat per la seva presentació pública.

Palma, novembre de 2010

Signat: David Gessner

Projectista

Signat: Julián Proenza Arenas

Co-director del projecte final de carrera

Signat: Manuel Alejandro Barranco González Co-director del projecte final de carrera

#### Resum

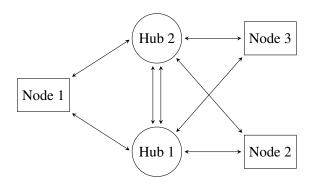

El protocol *Controller Area Network* (CAN) és amplament utilitzat en sistemes de control distribuïts. Però a pesar del seu ús extens, hi ha una controvèrsia sobre lo adequat que és CAN per sistemes que requereixen un grau de fiabilitat elevat. Aquesta controvèrsia es deguda principalment a una sèrie de limitacions de fiabilitat que té CAN, causades principalment per la topologia en bus que empra. Per superar aquestes limitacions, previ al projecte s'havien dissenyat dues topologies en estrella per CAN. La primera, *CANcentrate*, és una topologia en estrella simple amb un element central denominat concentrador (*hub*) que proporciona mecanismes per millorar la contenció d'errors. La segona, *ReCANcentrate*, és una topologia en estrella replicada, amb dos concentradors, que proporciona tolerància a fallades a més de proporcionar contenció d'errors.

Aquest projecte consisteix en la implementació d'un nou prototip de *ReCANcentrate*. Aquest nou prototip està basat en un prototip anterior que consistia en mostrar la viabilitat de implementar amb components comercials (*commercial off-the-shelf*) els concentradors de ReCANcentrate, així com mostrar que els mecanismes de contenció d'errors i tolerància a fallades dels concentradors funcionen correctament. El nou prototip en canvi té com a objectiu mostrar la viabilitat i la capacitat de tolerància a fallades dels nodes. Concretament, l'objectiu d'aquest projecte és la construcció del hardware d'un nou prototip, que consisteix en dos concentradors i tres nodes; la implementació d'un programa que faci de *driver* per als nodes del prototip; i la verificació, mitjançant experiments, de que els nodes poden tolerar tota una sèrie de fallades introduïdes mitjançant injecció de fallades.

# **Contents**

| 1. | Intro | oduction                                                       | 1  |

|----|-------|----------------------------------------------------------------|----|

|    | 1.1.  | Background and motivation                                      | 1  |

|    | 1.2.  | Goal of the project                                            | 3  |

|    | 1.3.  | Tasks realized                                                 | 3  |

|    | 1.4.  | Tasks <i>not</i> realized                                      | 5  |

|    | 1.5.  | Overview of the remaining chapters                             | 5  |

|    |       |                                                                |    |

| l. | Fo    | undations and previous work                                    | 7  |

| 2. | Intro | eduction to reliability, fault tolerance, and related concepts | ç  |

|    | 2.1.  | Basics                                                         | 9  |

|    | 2.2.  | Reliability and dependability                                  | 10 |

|    | 2.3.  | Fault tolerance                                                | 12 |

|    | 2.4.  | Implementation of fault-tolerant systems                       | 13 |

| 3. | Con   | troller Area Network (CAN)                                     | 15 |

|    | 3.1.  | CAN Physical Layer                                             | 15 |

|    | 3.2.  | CAN Data Link Layer                                            | 18 |

|    |       | 3.2.1. Frame format                                            | 18 |

|    |       | 3.2.2. Bit-wise arbitration mechanism                          | 21 |

|    |       | 3.2.3. Frame encoding                                          | 21 |

|    |       | 3.2.4. Error-signaling mechanism                               | 22 |

|    |       | 3.2.5. Error containment                                       | 24 |

|    |       | 3.2.6. Overload-signaling                                      | 24 |

|    | 3.3.  | CAN bit rate                                                   | 26 |

|    |       | 3.3.1. Synchronization                                         | 27 |

|    | 3.4.  | Reliability limitations of CAN                                 | 31 |

|    |       | 3.4.1. Limited error containment                               | 31 |

|    |       | 3.4.2. Limited support for fault tolerance                     | 32 |

|    |       | 3.4.3. Limited data consistency                                | 33 |

| 4. | CAN   | Icentrate                                                      | 37 |

|    | 4.1.  | Fault model for CAN and CANcentrate                            | 37 |

|    |       | CANcentrate's architecture                                     | 38 |

| 5.  | ReC   | ANcentrate                                                                                      | 43  |

|-----|-------|-------------------------------------------------------------------------------------------------|-----|

|     | 5.1.  | Fault model for ReCANcentrate                                                                   | 43  |

|     | 5.2.  | ReCANcentrate hub architecture                                                                  | 44  |

|     | 5.3.  | ReCANcentrate nodes                                                                             | 46  |

|     |       | 5.3.1. Media management in the absence of faults                                                | 47  |

|     |       | 5.3.2. Media management in the presence of faults                                               | 48  |

|     |       | 5.3.3. Driver architecture                                                                      | 49  |

|     |       | 5.3.4. Hardware requirements of the driver                                                      | 51  |

|     | 5.4.  | Previous ReCANcentrate prototype                                                                | 51  |

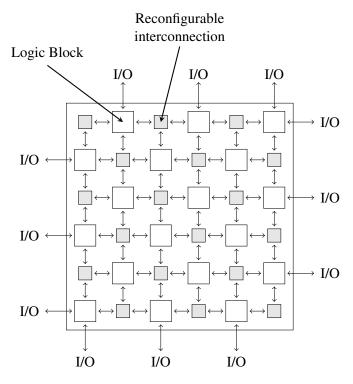

|     |       | 5.4.1. Brief introduction to FPGAs                                                              | 52  |

|     |       | 5.4.2. Hub implementation                                                                       | 52  |

|     |       | 5.4.3. Node implementation                                                                      | 53  |

|     |       | 5.4.4. Electronic circuits                                                                      | 55  |

|     |       |                                                                                                 |     |

| II. | Pro   | oject specific tasks                                                                            | 59  |

| 6.  | Eine  | ul decign of the modic management driver for the PoCAN centrate nodes                           | 61  |

| Ο.  |       | Il design of the media management driver for the ReCANcentrate nodes  Media management routines | 61  |

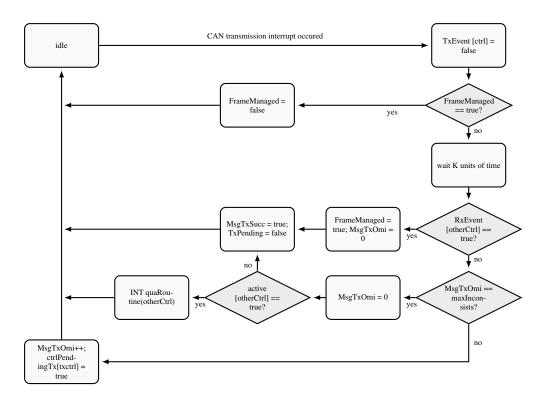

|     | 0.1.  | 6.1.1. The tx routine                                                                           | 62  |

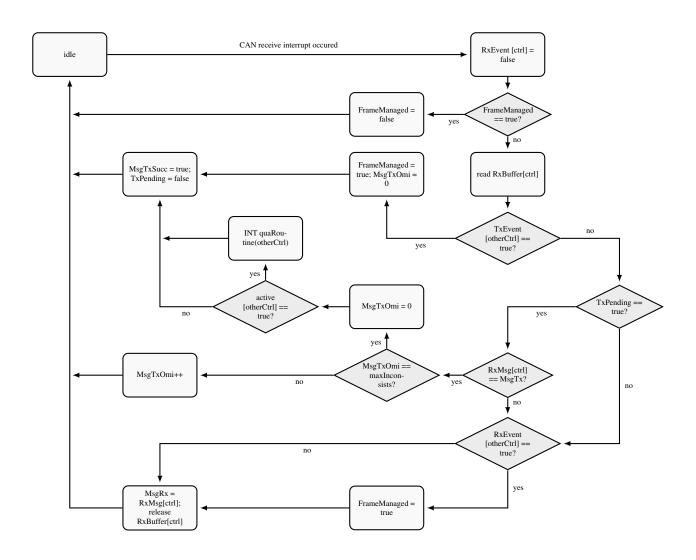

|     |       | 6.1.2. The rx routine                                                                           | 63  |

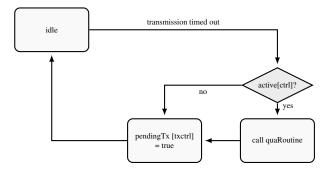

|     |       | 6.1.3. The qua routine                                                                          | 65  |

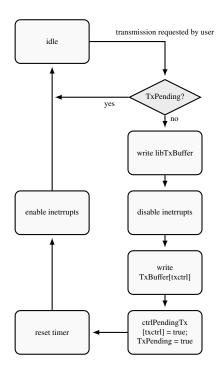

|     | 6.2.  | The tx request routine                                                                          | 67  |

|     | 6.3.  | Example executions                                                                              | 68  |

|     | 0.5.  | 6.3.1. Fault-free reception                                                                     | 68  |

|     |       | 6.3.2. Fault-free transmission                                                                  | 70  |

|     |       | 6.3.3. Example involving all four routines                                                      | 71  |

|     | 6.4.  | Fault-tolerance capacities of the media management driver                                       | 73  |

|     | 0. 1. | 6.4.1. Tolerance of the inconsistent message omission scenario identified by                    | 75  |

|     |       | Rufino, Veríssimo, Arroz, Almeida, and Rodrigues                                                | 73  |

|     |       | 6.4.2. Tolerance of the inconsistent message omission scenario identified by                    | , . |

|     |       | Proenza and Miro-Julia                                                                          | 76  |

| 7.  | New   | ReCANcentrate hardware prototype                                                                | 81  |

|     | 7.1.  | The wirewrap prototyping technique                                                              | 81  |

|     | 7.2.  | Implementation of the ReCANcentrate hubs                                                        | 82  |

|     | 7.3.  | Implementation of the ReCANcentrate nodes                                                       | 85  |

|     | 7.4.  | Testing the hardware of the prototype                                                           | 88  |

|     |       | 7.4.1. Verification of the electronic circuits                                                  | 88  |

|     |       | 7.4.2. Testing the node cores                                                                   | 88  |

|     |       | 7.4.3. Testing the node cores together with their I/O modules                                   | 89  |

|     |       | 7.4.4 Testing the hardware of the hubs                                                          | 90  |

| 8. | Impl   | ementation of the driver                                               | 93 |

|----|--------|------------------------------------------------------------------------|----|

|    | 8.1.   | Development environment                                                | 93 |

|    | 8.2.   | Methodology                                                            | 94 |

|    | 8.3.   | Overview of the driver source code                                     | 96 |

|    |        | 8.3.1. Implementation of assertions                                    | 96 |

|    |        |                                                                        | 97 |

|    |        | **                                                                     | 02 |

|    | 8.4.   |                                                                        | )4 |

| 9. | Test   | ng the driver on the hardware prototype 10                             | )7 |

|    | 9.1.   | Fault tolerance tests                                                  | )7 |

|    |        | 9.1.1. Implementation of fault injection                               | )7 |

|    |        | 9.1.2. Test programs                                                   | 10 |

|    |        | 9.1.3. Test strategy                                                   | 11 |

|    |        | 9.1.4. Stuck-at-recessive downlink                                     | 13 |

|    |        | 9.1.5. Stuck-at-recessive uplink                                       |    |

|    |        | 9.1.6. Stuck-at-dominant downlink                                      |    |

|    |        | 9.1.7. Stuck-at-dominant uplink                                        |    |

|    |        | 9.1.8. Tests that inject controller crashes                            |    |

|    | 9.2.   | Performance tests                                                      |    |

|    | ,      | 9.2.1. Methods to establish the worst-case execution time (WCET)       |    |

|    |        | 9.2.2. Performance measurement rationale                               |    |

|    |        | 9.2.3. Estimated worst-case scenario in terms of performance           |    |

|    |        | 9.2.4. Performance measurement of the estimated worst-case scenario 12 |    |

| 10 | . Con  | elusions 13                                                            | 33 |

|    |        | Summary                                                                |    |

|    |        | Future work                                                            | _  |

|    |        | Personal opinion                                                       |    |

|    |        | Publications                                                           |    |

| Δ  | Initia | I design of the media management driver for ReCANcentrate 14           | 11 |

|    |        |                                                                        |    |

| В. |        | ce code for the preliminary tests                                      | _  |

|    | B.1.   | Header files used by the preliminary tests                             | _  |

|    |        | B.1.1. can_aux.h                                                       |    |

|    |        | 6                                                                      | 46 |

|    |        | B.1.3. dspicdem.h                                                      |    |

|    |        | r                                                                      | 47 |

|    | B.2.   | · · · · · · · · · · · · · · · · · · ·                                  | 47 |

|    |        | · · · · · · · · · · · · · · · · · · ·                                  | 47 |

|    |        | B.2.2. canh_loopbk_int.c                                               |    |

|    | B.3.   | Single node test                                                       |    |

|    |        | B.3.1. one_node.c                                                      | 56 |

|    | B.4. | Simple AND-coupling module test       | 160                |

|----|------|---------------------------------------|--------------------|

|    |      | B.4.1. couplerModule.vhd              | 160                |

|    |      | B.4.2. couplerModule.ucf              | 161                |

|    |      | B.4.3. msg.h                          | 161                |

|    |      | B.4.4. receiver.c                     | 162                |

|    |      | B.4.5. transmitter.c                  | 163                |

| _  | Deix |                                       | 167                |

| C. |      |                                       | 1 <b>67</b><br>167 |

|    |      |                                       | 168                |

|    |      |                                       |                    |

|    |      |                                       | 169                |

|    |      |                                       | 185                |

|    |      |                                       | 190                |

|    |      |                                       | 192                |

|    |      |                                       | 193                |

|    |      | $\varepsilon$                         | 193                |

|    |      | · · · · · · · · · · · · · · · · · · · | 194                |

|    |      | · · · · · · · · · · · · · · · · · · · | 198                |

|    |      |                                       | 200                |

|    |      |                                       | 201                |

|    |      | 1                                     | 201                |

|    | C.14 | rxroutine.c                           | 204                |

|    | C.15 | rxroutine.h                           | 210                |

|    | C.16 | tracker.c                             | 210                |

|    | C.17 | txroutine.c                           | 214                |

|    | C.18 | tx_timer.c                            | 217                |

|    | C.19 | tx_timer.h                            | 218                |

| D. | ΔΡΙ  | source code 2                         | 221                |

| -  |      |                                       | 221                |

|    |      |                                       | 225                |

|    | D.2. | recancentate.ii                       | 223                |

| E. |      |                                       | 227                |

|    | E.1. | cancentrate.ucf                       | 227                |

| F. | Sou  | ce code for fault injection           | 231                |

|    | F.1. | Files to inject controller crashes    | 231                |

|    |      | •                                     | 231                |

|    |      |                                       | 231                |

|    | F.2. |                                       | 232                |

|    |      |                                       | 232                |

|    |      | •                                     | 236                |

|    |      | -                                     | 240                |

|    |      |                                       | -                  |

| G. | Sou  | rce code for the fault-tolerance tests  | 253 |

|----|------|-----------------------------------------|-----|

|    | G.1. | transmitter_3led_counter.c              | 253 |

|    | G.2. | transmitter_blinking_led.c              | 254 |

|    | G.3. | receiver.c                              | 255 |

| Н. | Sou  | rce code for the performance tests      | 259 |

|    | H.1. | 8byte_transmitter.c                     | 259 |

|    | H.2. | Obyte_transmitter.c                     | 260 |

| I. | Sou  | rce code for the profiler               | 261 |

|    | I.1. | profiler.c                              | 261 |

|    |      | profiler.h                              |     |

| J. | Stim | nulus files for the MPLAB SIM simulator | 265 |

|    | J.1. | c1omission_c2rxb1.sbs                   | 265 |

|    | J.2. | c1rxb0_c2rxb0_c1ewarn.sbs               |     |

|    | J.3. | c1rxb0_c2rxb1.sbs                       |     |

|    | J.4. | c1txb0_c2omission.sbs                   |     |

|    |      | c1txb0_c2rxb1.sbs                       |     |

# **List of Figures**

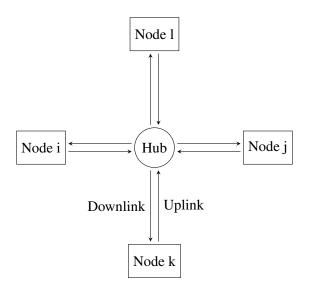

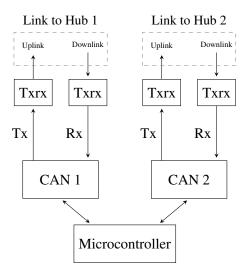

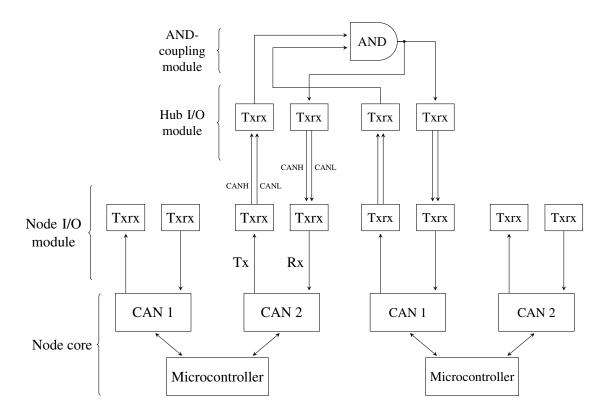

| 1.1.  | Architecture of ReCANcentrate for three nodes and two hubs                                                    | 2  |

|-------|---------------------------------------------------------------------------------------------------------------|----|

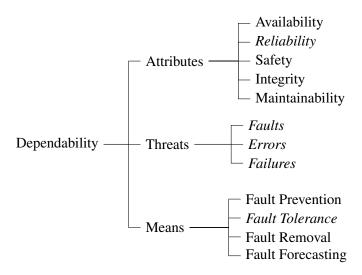

| 2.1.  | The dependability tree                                                                                        | 11 |

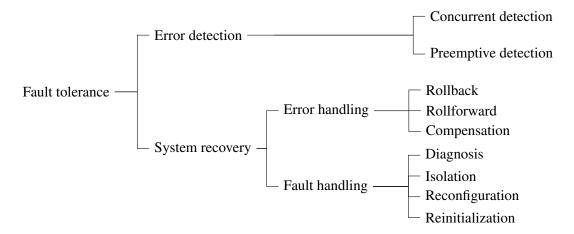

| 2.2.  | Fault tolerance techniques                                                                                    | 12 |

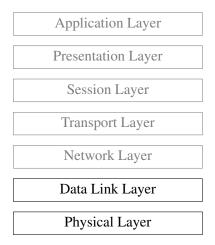

| 3.1.  | The ISO/OSI seven layer reference model                                                                       | 16 |

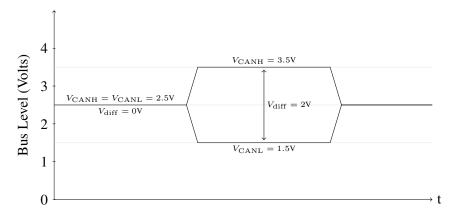

| 3.2.  | CAN bus level                                                                                                 | 17 |

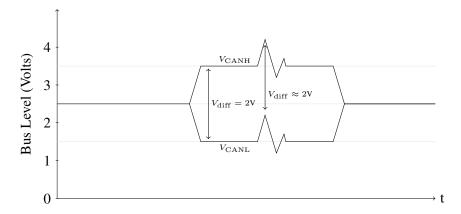

| 3.3.  | CAN bus level with EMI                                                                                        | 17 |

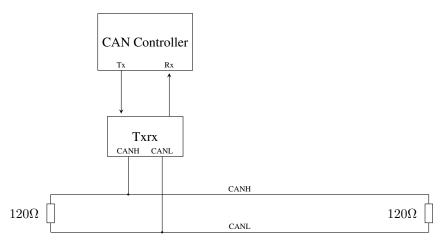

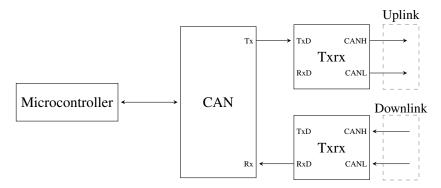

| 3.4.  | Connecting a CAN controller to a CAN bus through a CAN transceiver                                            | 18 |

| 3.5.  | CAN standard data frame format                                                                                | 19 |

| 3.6.  | CAN standard remote frame format                                                                              | 20 |

| 3.7.  | CAN arbitration example                                                                                       | 22 |

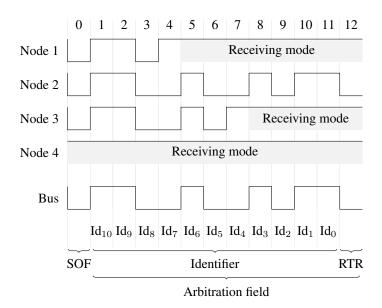

| 3.8.  | Example of CAN's error-signaling mechanism                                                                    | 23 |

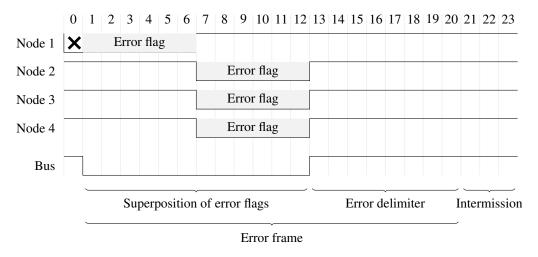

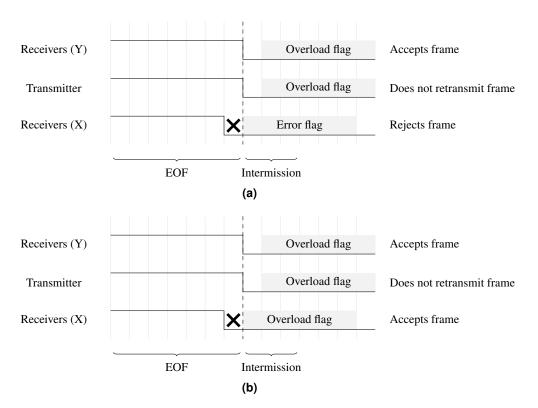

| 3.9.  | Example of CAN's overload-signaling mechanism                                                                 | 25 |

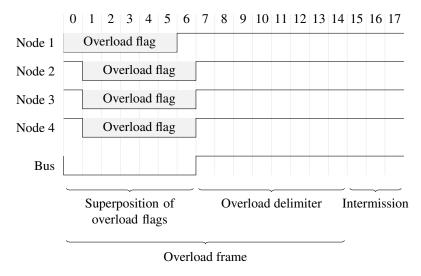

| 3.10. | Bit time segments.                                                                                            | 26 |

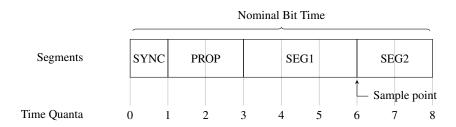

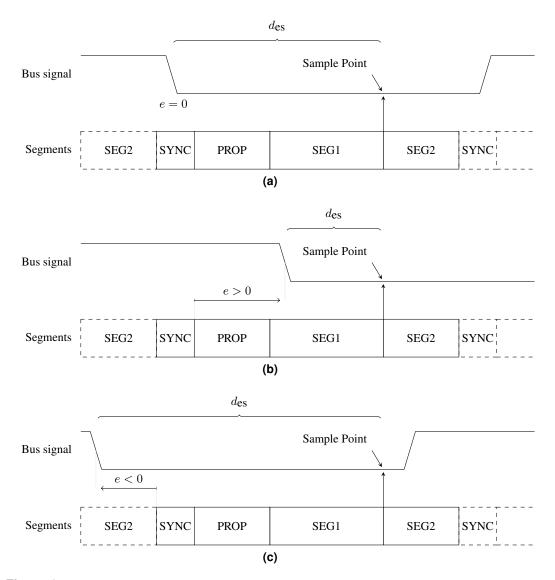

| 3.11. | Possible phase errors of an edge in CAN                                                                       | 29 |

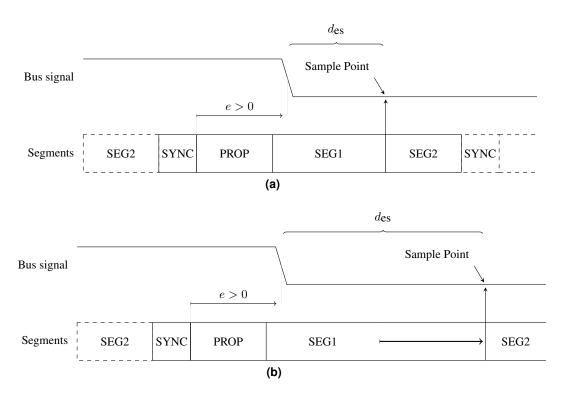

| 3.12. | Resynchronization of a positive phase error in CAN                                                            | 30 |

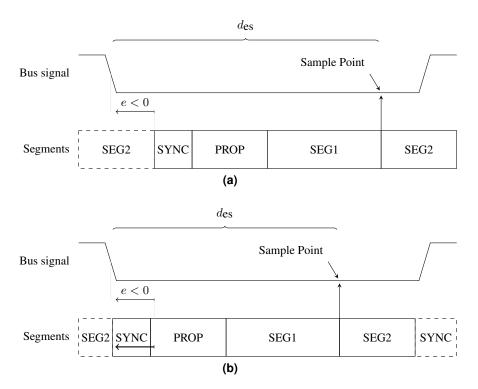

| 3.13. | Resynchronization of a negative phase error in CAN                                                            | 31 |

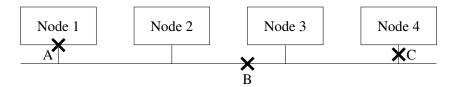

| 3.14. | Sample faults in a CAN bus                                                                                    | 32 |

| 3.15. | CAN's last bit rule                                                                                           | 34 |

|       | Inconsistent message duplication scenario discussed by Rufino et al. [1998] and Proenza and Miro-Julia [2000] | 35 |

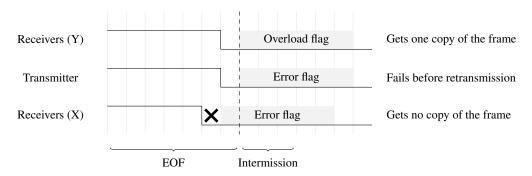

| 3.17. | Inconsistent message omission scenario identified by Rufino et al. [1998]                                     | 36 |

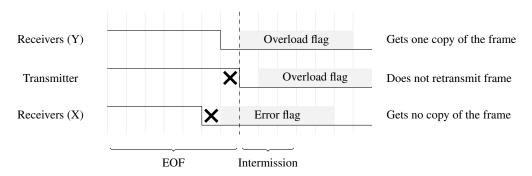

|       | Inconsistent message omission scenario identified by Proenza and Miro-Julia                                   |    |

|       | [2000]                                                                                                        | 36 |

| 4.1.  | CANcentrate's architecture for four nodes                                                                     | 39 |

| 4.2.  | CANcentrate node architecture                                                                                 | 40 |

| 4.3.  | Internal structure of a CANcentrate hub                                                                       | 41 |

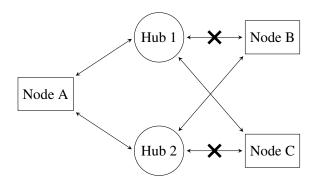

| 5.1.  | Example of a <i>network partition</i> fault                                                                   | 44 |

| 5.2.  | ReCANcentrate's architecture                                                                                  | 44 |

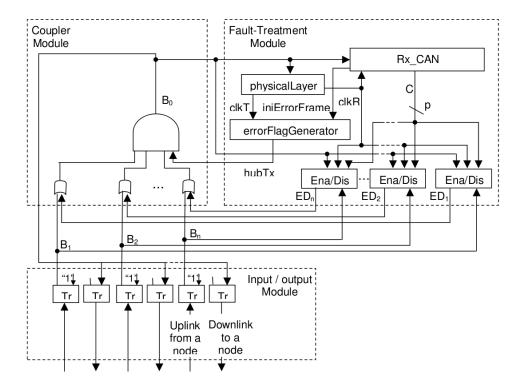

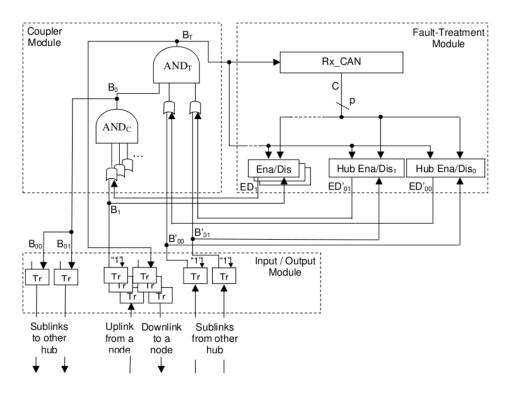

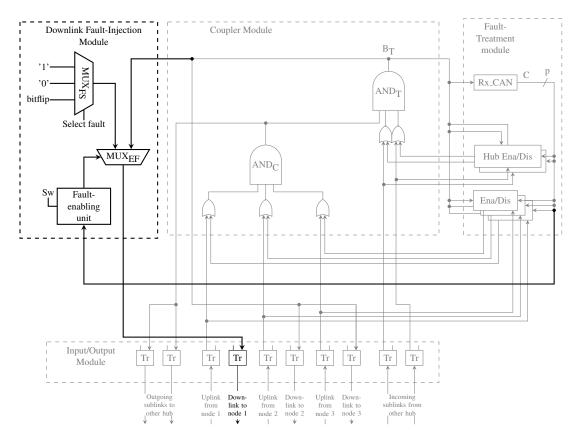

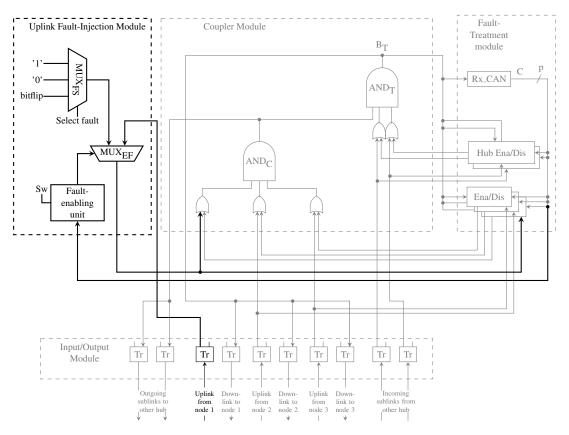

| 5.3.  | Internal structure of a ReCANcentrate hub                                                                     | 45 |

| 5.4.  | ReCANcentrate node architecture                                                                               | 47 |

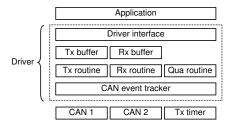

| 5.5.  | Basic driver structure                                                                                        | 50 |

| 5.6.  | Internal structure of a field-programmable gate array (FPGA)                                                  | 53 |

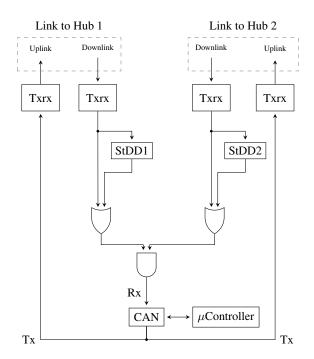

| 5.7.  | ReCANcentrate node architecture using an approach inspired by Rufino, Veríssimo,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|       | and Arroz [1999]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 54  |

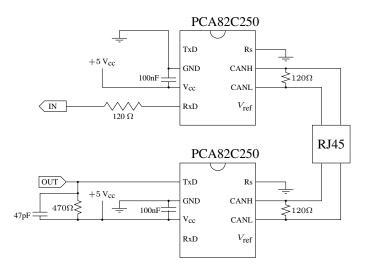

| 5.8.  | Electronic circuit for a port of the I/O module of a hub or node                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 56  |

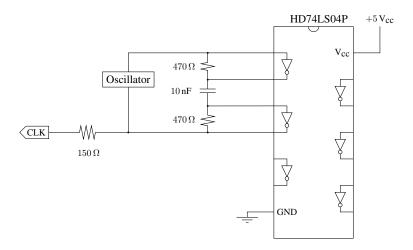

| 5.9.  | Electronic circuit to attach an external oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 57  |

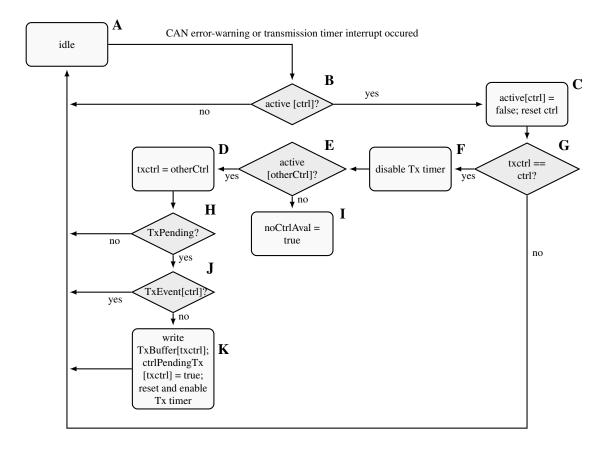

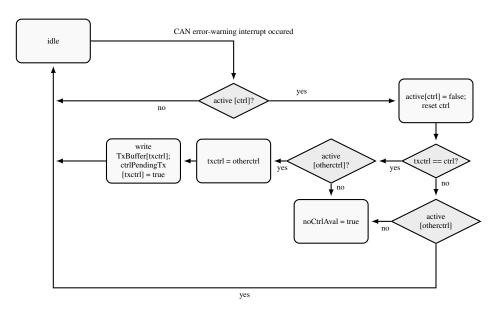

| 6.1.  | Final design of the <i>tx routine</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 62  |

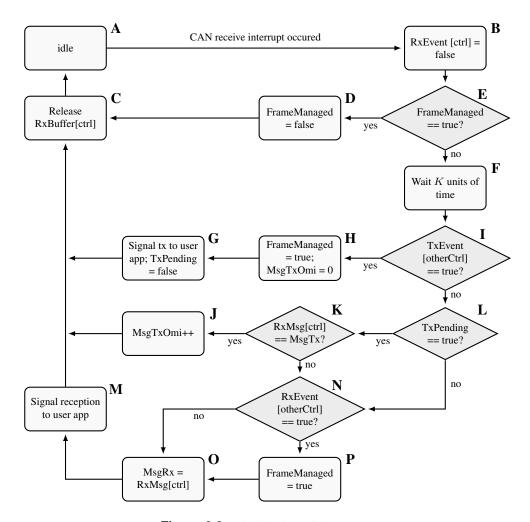

| 6.2.  | Final design of the <i>rx routine</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 64  |

| 6.3.  | Final design of the <i>qua routine</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 66  |

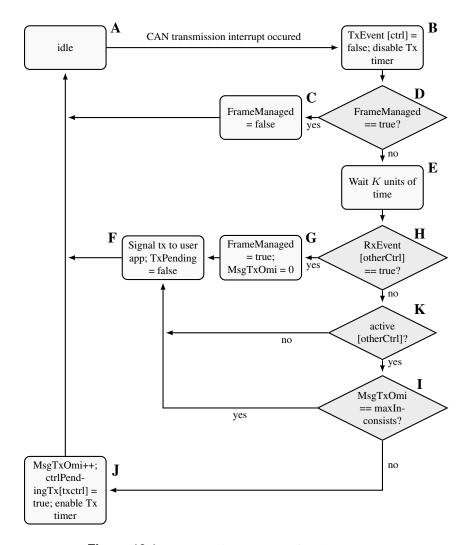

| 6.4.  | Final design of the <i>tx request</i> routine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 67  |

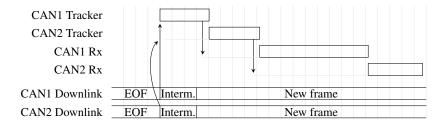

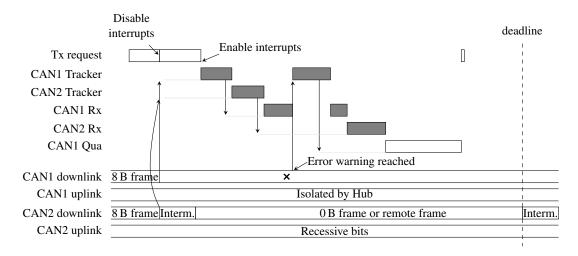

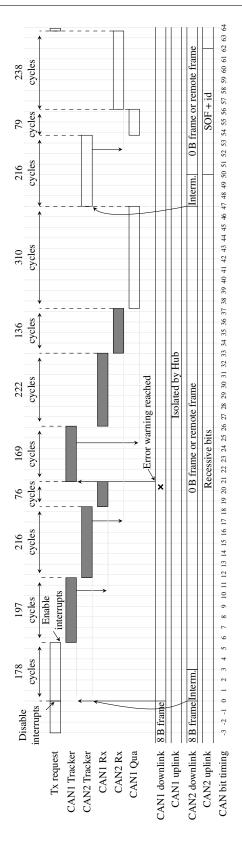

| 6.5.  | Example execution of the reception of a data frame                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 68  |

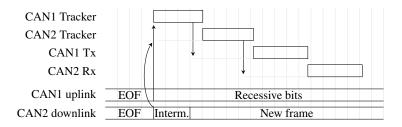

| 6.6.  | Example execution of the transmission of a frame                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 70  |

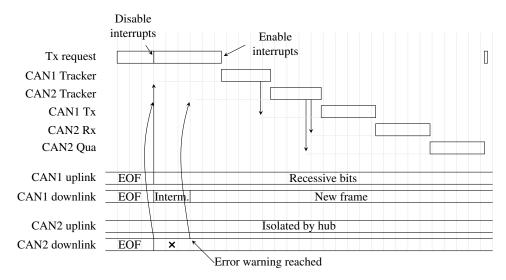

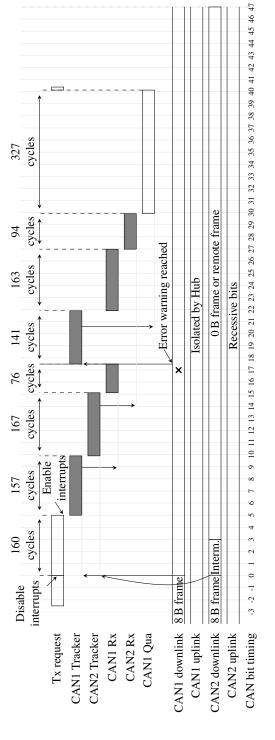

| 6.7.  | Example execution involving a tx request, a rx routine, a tx routine, and a qua                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 71  |

| 6.8.  | routine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | /1  |

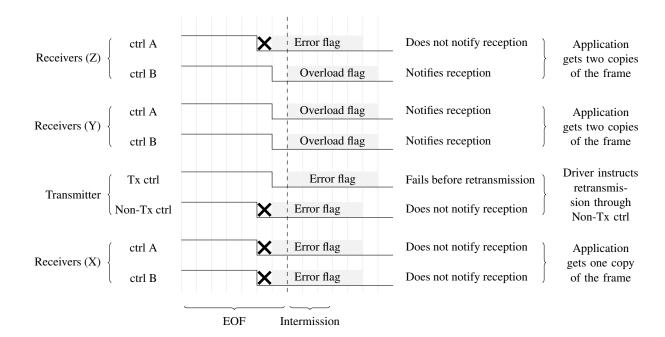

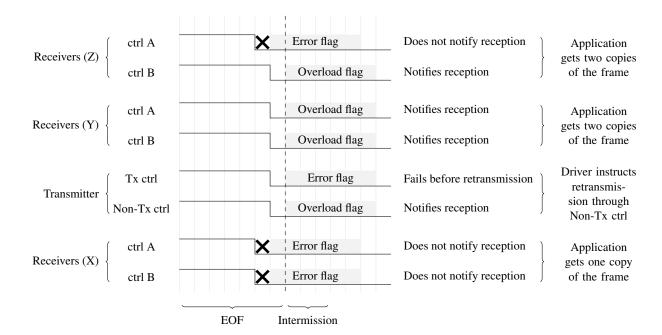

|       | et al. in ReCANcentrate (case 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 74  |

| 6.9.  | Management of the inconsistent message omission scenario identified by Rufino                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

|       | et al. in ReCANcentrate (case 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 76  |

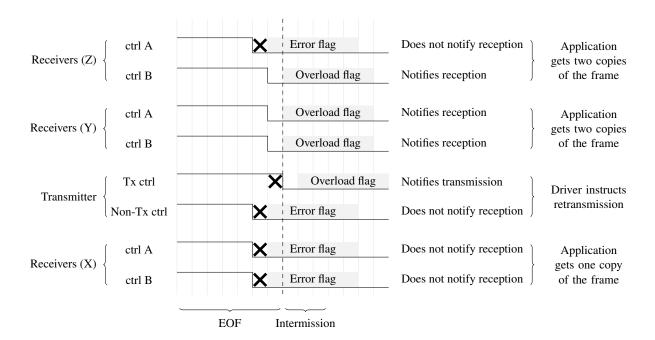

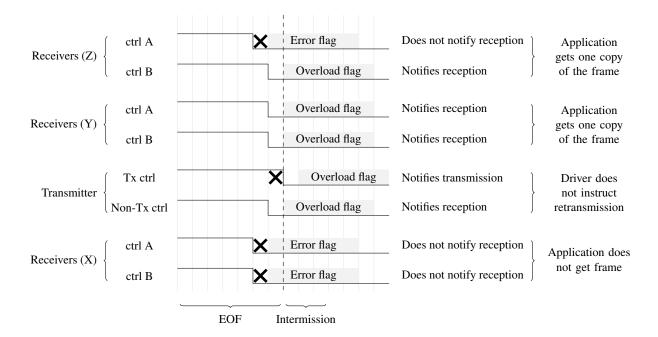

| 6.10. | Case where the inconsistent message omission scenario identified by Proenza                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|       | and Miro-Julia is avoided in ReCANcentrate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 77  |

| 6.11. | Case where the inconsistent message omission scenario identified by Proenza                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|       | and Miro-Julia is <i>not</i> avoided in ReCANcentrate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 78  |

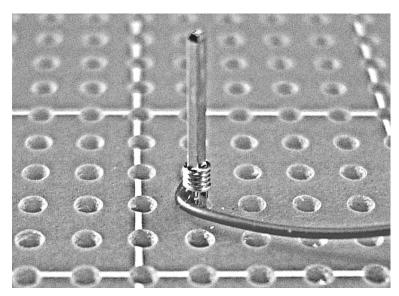

| 7.1.  | Pin with a wire connected to it through wirewrapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 81  |

| 7.2.  | Manual wirewrapping tool and wirewrapping wire                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 82  |

| 7.3.  | Implementation of a ReCANcentrate hub, showing its main building blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 83  |

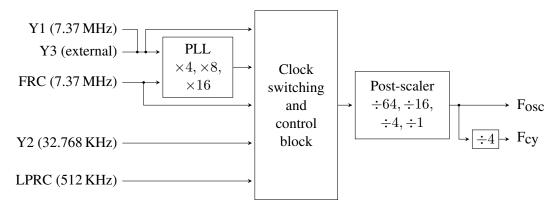

| 7.4.  | Clock sources in a dsPICDEM prototyping board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 87  |

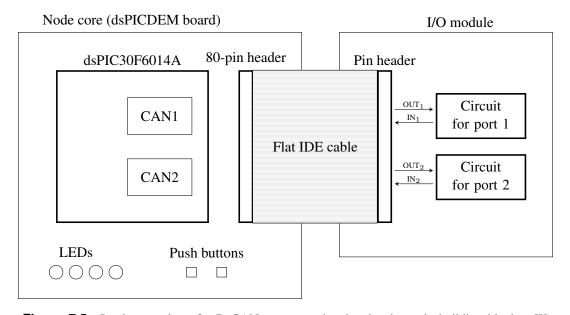

| 7.5.  | Implementation of a ReCANcentrate node, showing its main building blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 87  |

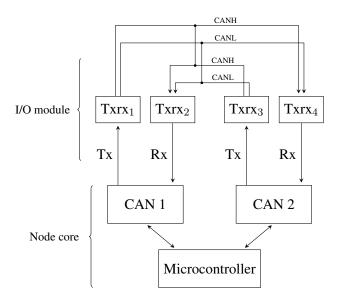

| 7.6.  | Connecting the two CAN controllers of a single ReCANcentrate node to each                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

|       | other                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 89  |